The key research questions that we target here are:

1. How can we settle the trade-off between large sinal bandwidth and power-efficiency?

2. What are the key SDM architectural choices that increase signal bandwidth, maintain low powe consumption, while achieving a compatitive linearity to the Nyquist ADC?

Our key research hypotheses are:

1. SDM with low OSR for power-efficiency;

2. Multi-bit, multi-stage SDM for large Dynamic-Ranges;

3. Power efficient circuits.

Theses:

Broadband Continuous-Time MASH Sigma-Delta ADCs

Papers:

Analysis of the Inter-Stage Signal Leakage in Wide BW Low OSR and High DR CT MASH ΔΣM

Novel Baseband Analog Beamforming through Resistive DACs and Sigma Delta Modulators

A 1.9 mW 250 MHz Bandwidth Continuous-Time ΣΔ Modulator for Ultra-Wideband Applications

A 2 GHz 0.98 mW 4-bit SAR-based quantizer with ELD compensation in an UWB CT ΣΔ modulator

Current-mode multi-path excess loop delay compensation for GHz sampling CT ΣΔ ADCs

A digital calibration technique for wide-band CT MASH ΣΔ ADCs with relaxed filter requirements

New introduction youtube video by Qilong Liu!

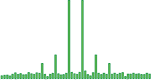

Schreier FOM calculator

The Analog-to-Digital conversion function

Analog to Digital Conversion (ADC) is the function of converting an analog signal, being continuous in both amplitude and time, such as an audio or video signal, into a digital abstract representation, being discrete in both amplitude and time. This is accomplished by limiting the bandwidth ofthe analog signal, sampling it at regular time intervals and quantizing the amplitude of each sample to a finite number of digital values. The ADC is a fundamental building block in many electronic systems, including audio and video processing, communication systems, and data acquisition systems.

At high-speeds, the ADC integrated implementation needs to address major challenges in order to maintain accurate and reliable performance. Key problems are:

- Sampling rate: High speed ADCs require high sampling rates, which can result in increased power consumption (e.g. clock propagation networks), reduced linearity, and increased disturbances.

- Effective-Number-Of-Bits (ENOB) vs Bandwidth (BW): Various analog design limitations at high-speeds, such as finite bandwidth, time-constants, signal dependent reistance, charge and clock feedthrough, lead to reduced accuracy, dynamic range and bandwidth. Notably, kT/C noise of the S/H block is an example of the trande-off between ENOB and BW. To minimize kT/C noise, a large C is required. A large C, would increase the time constant of the S/H block and reduce the BW. A reduced BW would lead to logner settling, and hence signal-dependent errors, which reduces the ENOB via non-linearity errors.

- High-speed ADCs are suffer from non-linearity errors, which cause significant distortion in the converted digital signal.

- Bandwidth: High-speed ADCs must have an Anti-Aliasing Filter and driver with wide bandwidth to accurately get fast-changing signals.

- Power consumption: High-speed ADCs consume more power than lower-speed devices, which can be a concern in battery-powered systems or in high-density applications. Notably the power efficiency and hence the FoMs are much lower at high-speeds.

- Clock jitter: Clock jitter, or fluctuations in the timing of the ADC's clock signal, can cause noise-like errors in the converted digital signal and reduce overall accuracy.

To overcome such challenges, advanced ADC architectures and technologies, such as SDM, flash ADCs, and pipeline ADCs, are commonly used in high-speed applications.

Sigma-delta modulation is a type of analog-to-digital conversion (ADC) technique based on the principles of oversampling and noise shaping. The main idea of SDM is to quantize an analog signal by oversampling the signal and using feedback to shape the errors, like the quantization noise.

In an SDM ADC, the analog signal is first filtered and then sampled at a higher rate than the required Nyquist rate. The oversampled signal is then quantized using a quantizer, resulting in a high-frequency, high-level quantization noise.

The key benefit of sigma-delta modulation is its ability to provide high-resolution quantization of the signal, even with low-resolution quantization stages. This makes it a popular technique for high-speed and low-power ADC applications, especially in audio and multimedia applications. However, we push this concept to application that require wide signal bandwidths, such wirless links and automotive radars.